Raspberry Pi Unveils PCIe FFC Connector and New HAT+ Specifications

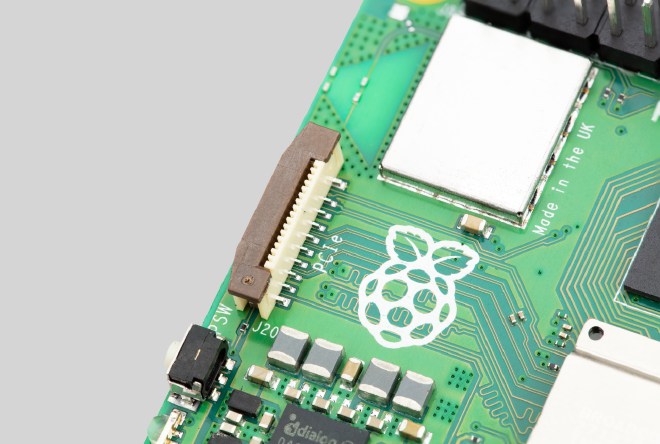

One of the most notable features of the new Raspberry Pi platform is its small, vertical, 16-way FFC (Flat Flexible Cable) connector on the left-hand side of the board. This connector exposes a single-lane PCI Express interface.

The Peripheral Component Interconnect Express (PCI Express or PCIe) is a board-level interconnect that enables high-speed data transfer between a processor chip and external peripherals such as NVMe SSDs, Ethernet cards, and AI/ML accelerators. PCIe achieves this by serializing data transfers and sending one bit at a time down a single channel. Each channel consists of one or more differential pairs on the PCB, which are controlled waveguides made by closely spaced wires. In the case of a single-lane PCIe interface, there is a single transmit pair, a single receive pair, and a clock pair, requiring three differential pairs and six wires. The Raspberry Pi 5, based on the BCM2712 processor, is connected to the RP1 I/O controller via an ×4 interface.

The PCIe specification also requires sideband signals such as reset, clock request, and wakeup. The 16-way connector on the Raspberry Pi provides all these signals, along with two pins for controlling board power and automatically detecting a properly designed PIP (PCIe Peripheral) by the Raspberry Pi firmware.

Instead of adding an M.2 connector to the Raspberry Pi 5, which would be large, relatively expensive, and require a 3.3V, 3A power supply, the Raspberry Pi team opted for a small, low-cost FFC connector. This allowed them to provide a PCIe interface without increasing the board size or imposing additional costs on users.

At the launch of the Raspberry Pi 5, the team did not have a specification for building peripherals that attach to the 16-way PCIe connector. They wanted to thoroughly test their own prototype product and consider the interaction of PCIe peripherals with Raspberry Pi power states and firmware. They have now released the first revision of the specification and are in the final stage of prototyping their own M.2 M Key HAT+. This HAT+ will be launched early next year.

In addition to the PCIe connector specification, the Raspberry Pi team has also released a preliminary version of the new HAT+ specification. The original HAT specification, written in 2014, is in need of an update. The new specification simplifies certain aspects, including the required EEPROM contents, and consolidates everything into one document. It also adds new features. While there is still work to be done on this standard and the EEPROM utilities have not been updated, this release provides a glimpse into the changes in the HAT standard.

The Raspberry Pi team wanted to ensure that the HAT+ standard is developed correctly, as it is expected to be in use for as long as the old HAT standard. They believe that PCIe boards (PIPs) that go on top of the Raspberry Pi should be HAT+ boards, and their own M.2 HAT+ will adhere to this standard.

More information can be found in the first revision of the Raspberry Pi Connector for PCIe datasheet, and the Raspberry Pi HAT+ Specification datasheet.